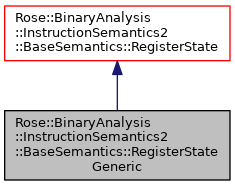

Description

A RegisterState for any architecture.

This state stores a list of non-overlapping registers and their values, typically only for the registers that have been accessed. The state automatically switches between different representations when accessing a register that overlaps with one or more stored registers (see the accessModifiesExistingLocations and accessCreatesLocations properties). For instance, if the state stores 64-bit registers and the specimen suddently switches to 32-bit mode, this state will split the 64-bit registers into 32-bit pieces. If the analysis later returns to 64-bit mode, the 32-bit pieces are concatenated back to 64-bit values. This splitting and concatenation occurs on a per-register basis at the time the register is read or written.

The register state also stores optional information about writers for each register. Writer information (addresses of instructions that wrote to the register) are stored as sets defined at each bit of the register. This allows a wide register, like x86 RAX, to be written to in parts by different instructions, like x86 AL. The register state itself doesn't update this information automatically–it only provides the API by which a higher software layer can manipulate the information. This design allows the writer data structure to alternatively be used for things other than addresses of writing instructions. For instance, the SymbolicSemantics::RiscOperators has a setting that enables tracking writers.

Definition at line 40 of file BaseSemantics/RegisterStateGeneric.h.

#include <Rose/BinaryAnalysis/InstructionSemantics2/BaseSemantics/RegisterStateGeneric.h>

Classes | |

| class | AccessCreatesLocationsGuard |

| Guards whether access is able to create new locations. More... | |

| class | AccessModifiesExistingLocationsGuard |

| Guards whether access can change set of existing locations. More... | |

| class | RegisterNotPresent |

| Exception when register storage is not present. More... | |

| struct | RegPair |

| A register descriptor and its value. More... | |

| struct | RegStore |

| Register map keys. More... | |

| class | Visitor |

| Functors for traversing register values in a register state. More... | |

Public Member Functions | |

| virtual RegisterStatePtr | create (const SValuePtr &protoval, const RegisterDictionary *regdict) const override |

| Virtual constructor. More... | |

| virtual RegisterStatePtr | clone () const override |

| Make a copy of this register state. More... | |

| virtual void | clear () override |

| Removes stored values from the register state. More... | |

| virtual void | zero () override |

| Set all registers to the zero. More... | |

| virtual SValuePtr | readRegister (RegisterDescriptor, const SValuePtr &dflt, RiscOperators *) override |

| Read a value from a register. More... | |

| virtual SValuePtr | peekRegister (RegisterDescriptor, const SValuePtr &dflt, RiscOperators *) override |

| Read a register without side effects. More... | |

| virtual void | writeRegister (RegisterDescriptor, const SValuePtr &value, RiscOperators *) override |

| Write a value to a register. More... | |

| virtual void | print (std::ostream &, Formatter &) const override |

| Print the register contents. More... | |

| virtual bool | merge (const RegisterStatePtr &other, RiscOperators *) override |

| Merge register states for data flow analysis. More... | |

| virtual void | hash (Combinatorics::Hasher &, RiscOperators *) const override |

| Hash the register state. More... | |

| virtual void | initialize_large () |

| Initialize all registers of the dictionary. More... | |

| virtual void | initialize_small () |

| Initialize all registers of the dictionary. More... | |

| void | initialize_nonoverlapping (const std::vector< RegisterDescriptor > &, bool initialize_to_zero) |

| Initialize the specified registers of the dictionary. More... | |

| virtual RegPairs | get_stored_registers () const |

| Returns the list of all registers and their values. More... | |

| virtual bool | is_partly_stored (RegisterDescriptor) const |

| Determines if some of the specified register is stored in the state. More... | |

| virtual bool | is_wholly_stored (RegisterDescriptor) const |

| Determines if the specified register is wholly stored in the state. More... | |

| virtual bool | is_exactly_stored (RegisterDescriptor) const |

| Determines if the specified register is stored exactly in the state. More... | |

| virtual ExtentMap | stored_parts (RegisterDescriptor) const |

| Returns a description of which bits of a register are stored. More... | |

| virtual RegPairs | overlappingRegisters (RegisterDescriptor) const |

| Find stored registers overlapping with specified register. More... | |

| virtual void | erase_register (RegisterDescriptor, RiscOperators *) |

| Cause a register to not be stored. More... | |

| virtual void | traverse (Visitor &) |

| Traverse register/value pairs. More... | |

| virtual AddressSet | getWritersUnion (RegisterDescriptor) const |

| Get writer information. More... | |

| virtual AddressSet | getWritersIntersection (RegisterDescriptor) const |

| Get writer information. More... | |

| virtual bool | insertWriters (RegisterDescriptor, const AddressSet &writerVas) |

| Insert writer information. More... | |

| virtual void | eraseWriters (RegisterDescriptor, const AddressSet &writerVas) |

| Erase specified writers. More... | |

| virtual void | setWriters (RegisterDescriptor, const AddressSet &writers) |

| Set writer information. More... | |

| virtual bool | insertProperties (RegisterDescriptor, const InputOutputPropertySet &) |

| Insert Boolean properties. More... | |

| virtual bool | eraseProperties (RegisterDescriptor, const InputOutputPropertySet &) |

| Erase Boolean properties. More... | |

| virtual void | setProperties (RegisterDescriptor, const InputOutputPropertySet &) |

| Assign property set. More... | |

| virtual std::vector< RegisterDescriptor > | findProperties (const InputOutputPropertySet &required, const InputOutputPropertySet &prohibited=InputOutputPropertySet()) const |

| Get registers having certain properties. More... | |

| virtual void | updateWriteProperties (RegisterDescriptor, InputOutputProperty) |

| Update write properties. More... | |

| virtual void | updateReadProperties (RegisterDescriptor) |

| Update read properties. More... | |

| bool | accessModifiesExistingLocations () const |

| Property: Whether stored registers are adapted to access patterns. More... | |

| virtual void | accessModifiesExistingLocations (bool b) |

| Property: Whether stored registers are adapted to access patterns. More... | |

| bool | accessCreatesLocations () const |

| Property: Whether access can create new locations. More... | |

| virtual void | accessCreatesLocations (bool b) |

| Property: Whether access can create new locations. More... | |

| virtual bool | hasWritersAny (RegisterDescriptor) const |

| Whether a register has writers. More... | |

| virtual bool | hasWritersAll (RegisterDescriptor) const |

| Whether a register has writers. More... | |

| virtual void | eraseWriters (RegisterDescriptor) |

| Erase all writers. More... | |

| virtual void | eraseWriters () |

| Erase all writers. More... | |

| virtual bool | hasPropertyAny (RegisterDescriptor, InputOutputProperty) const |

| Whether a register has the specified property. More... | |

| virtual bool | hasPropertyAll (RegisterDescriptor, InputOutputProperty) const |

| Whether a register has the specified property. More... | |

| virtual InputOutputPropertySet | getPropertiesUnion (RegisterDescriptor) const |

| Get properties. More... | |

| virtual InputOutputPropertySet | getPropertiesIntersection (RegisterDescriptor) const |

| Get properties. More... | |

| virtual void | eraseProperties (RegisterDescriptor) |

| Erase all Boolean properties. More... | |

| virtual void | eraseProperties () |

| Erase all Boolean properties. More... | |

Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState | |

| SValuePtr | protoval () const |

| Return the protoval. More... | |

| const RegisterDictionary * | get_register_dictionary () const ROSE_DEPRECATED("use registerDictionary property") |

| void | set_register_dictionary (const RegisterDictionary *rd) ROSE_DEPRECATED("use registerDictionary property") |

| MergerPtr | merger () const |

| Property: Merger. More... | |

| void | merger (const MergerPtr &m) |

| Property: Merger. More... | |

| const RegisterDictionary * | registerDictionary () const |

| Property: Register dictionary. More... | |

| void | registerDictionary (const RegisterDictionary *rd) |

| Property: Register dictionary. More... | |

| void | print (std::ostream &stream, const std::string prefix="") const |

| Print the register contents. More... | |

| WithFormatter | with_format (Formatter &fmt) |

| Used for printing register states with formatting. More... | |

| WithFormatter | operator+ (Formatter &fmt) |

| Used for printing register states with formatting. More... | |

| WithFormatter | operator+ (const std::string &linePrefix) |

| Used for printing register states with formatting. More... | |

Static Public Member Functions | |

| static RegisterStateGenericPtr | instance (const SValuePtr &protoval, const RegisterDictionary *regdict) |

| Instantiate a new register state. More... | |

| static RegisterStateGenericPtr | instance (const RegisterStateGenericPtr &other) |

| Instantiate a new copy of an existing register state. More... | |

| static RegisterStateGenericPtr | promote (const RegisterStatePtr &from) |

| Run-time promotion of a base register state pointer to a RegisterStateGeneric pointer. More... | |

Static Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState Static Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState | |

| static RegisterStatePtr | promote (const RegisterStatePtr &x) |

Protected Member Functions | |

| RegisterStateGeneric (const SValuePtr &protoval, const RegisterDictionary *regdict) | |

| RegisterStateGeneric (const RegisterStateGeneric &other) | |

| void | deep_copy_values () |

| void | scanAccessedLocations (RegisterDescriptor reg, RiscOperators *ops, RegPairs &accessedParts, RegPairs &preservedParts) const |

| void | clearOverlappingLocations (RegisterDescriptor) |

| void | assertStorageConditions (const std::string &where, RegisterDescriptor what) const |

Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState | |

| RegisterState (const SValuePtr &protoval, const RegisterDictionary *regdict) | |

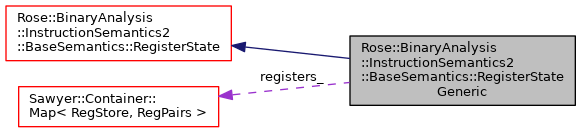

Protected Attributes | |

| Registers | registers_ |

| Values for registers that have been accessed. More... | |

Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState | |

| const RegisterDictionary * | regdict |

| Registers that are able to be stored by this state. More... | |

Member Typedef Documentation

| using Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::Super = RegisterState |

Base type.

Definition at line 46 of file BaseSemantics/RegisterStateGeneric.h.

| using Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::Ptr = RegisterStateGenericPtr |

Shared-ownership pointer.

Definition at line 49 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::Interval<size_t> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::BitRange |

A range of bits indexes.

Represents of contiguous interval of bit indexes, such as all bits numbered zero through 15, inclusive.

Definition at line 65 of file BaseSemantics/RegisterStateGeneric.h.

| typedef std::vector<RegPair> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::RegPairs |

Vector of register/value pairs.

Definition at line 125 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::Map<RegStore, RegPairs> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::Registers |

Values for all registers.

Definition at line 128 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::IntervalSetMap<BitRange, InputOutputPropertySet> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::BitProperties |

Boolean properties per bit.

This container stores properties per bit of a major/minor register pair. For instance, the x86 16-bit AX register might have different sets of properties for its different subregisters, AL and AH. This container stores those sets per bit.

Definition at line 140 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::Map<RegStore, BitProperties> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::RegisterProperties |

Boolean properties for all registers.

This container is indexed by register major/minor pair, then by a bit number, and stores a set of properties.

Definition at line 145 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::Set<rose_addr_t> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::AddressSet |

Set of virtual addresses.

Definition at line 153 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::IntervalSetMap<BitRange, AddressSet> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::BitAddressSet |

Virtual addresses per bit.

Definition at line 156 of file BaseSemantics/RegisterStateGeneric.h.

| typedef Sawyer::Container::Map<RegStore, BitAddressSet> Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::RegisterAddressSet |

Virtual addresses for all registers.

Definition at line 159 of file BaseSemantics/RegisterStateGeneric.h.

Member Function Documentation

|

inlinestatic |

Instantiate a new register state.

The protoval argument must be a non-null pointer to a semantic value which will be used only to create additional instances of the value via its virtual constructors. The prototypical value is normally of the same type for all parts of a semantic analysis: its state and operator classes.

The register dictionary, regdict, describes the registers that can be stored by this register state, and should be compatible with the register dictionary used for other parts of binary analysis.

Definition at line 232 of file BaseSemantics/RegisterStateGeneric.h.

Referenced by create(), Rose::BinaryAnalysis::InstructionSemantics2::LlvmSemantics::RiscOperators::instance(), Rose::BinaryAnalysis::Partitioner2::Semantics::RiscOperators::instance(), Rose::BinaryAnalysis::InstructionSemantics2::SourceAstSemantics::RiscOperators::instance(), Rose::BinaryAnalysis::InstructionSemantics2::IntervalSemantics::RiscOperators::instance(), Rose::BinaryAnalysis::InstructionSemantics2::ConcreteSemantics::RiscOperators::instance(), and Rose::BinaryAnalysis::InstructionSemantics2::SymbolicSemantics::RiscOperators::instance().

|

inlinestatic |

Instantiate a new copy of an existing register state.

Definition at line 237 of file BaseSemantics/RegisterStateGeneric.h.

|

inlineoverridevirtual |

Virtual constructor.

The protoval argument must be a non-null pointer to a semantic value which will be used only to create additional instances of the value via its virtual constructors. The prototypical value is normally of the same type for all parts of a semantic analysis. The register state must be compatible with the rest of the binary analysis objects in use.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

Definition at line 246 of file BaseSemantics/RegisterStateGeneric.h.

References instance().

|

inlineoverridevirtual |

Make a copy of this register state.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

Definition at line 250 of file BaseSemantics/RegisterStateGeneric.h.

|

inlinestatic |

Run-time promotion of a base register state pointer to a RegisterStateGeneric pointer.

This is a checked conversion–it will fail if from does not point to a RegisterStateGeneric object.

Definition at line 260 of file BaseSemantics/RegisterStateGeneric.h.

|

inline |

Property: Whether stored registers are adapted to access patterns.

When accessing an existing register for read or write, the register state can adapt the list of existing storage locations to match the access pattern. For instance, accessing the middle of a register could split the register into three storage locations or leave it as one. Similarly accessing a register that spans two or more storage locations could either concatenate them into one location or leave them separate.

When this property is true then existing storage locations can be modified, otherwise extra steps are taken to preserve the list of storage locations.

This property applies only to readRegister and writeRegister and not to those methods that are not typically called as part of processing instruction semantics.

Definition at line 285 of file BaseSemantics/RegisterStateGeneric.h.

|

inlinevirtual |

Property: Whether stored registers are adapted to access patterns.

When accessing an existing register for read or write, the register state can adapt the list of existing storage locations to match the access pattern. For instance, accessing the middle of a register could split the register into three storage locations or leave it as one. Similarly accessing a register that spans two or more storage locations could either concatenate them into one location or leave them separate.

When this property is true then existing storage locations can be modified, otherwise extra steps are taken to preserve the list of storage locations.

This property applies only to readRegister and writeRegister and not to those methods that are not typically called as part of processing instruction semantics.

Definition at line 286 of file BaseSemantics/RegisterStateGeneric.h.

|

inline |

Property: Whether access can create new locations.

This property controls what happens if some part of a register is accessed that isn't stored in the state. If the property is true then that part of the register springs into existence, otherwise an RegisterNotPresent exception is thrown.

Definition at line 313 of file BaseSemantics/RegisterStateGeneric.h.

|

inlinevirtual |

Property: Whether access can create new locations.

This property controls what happens if some part of a register is accessed that isn't stored in the state. If the property is true then that part of the register springs into existence, otherwise an RegisterNotPresent exception is thrown.

Definition at line 314 of file BaseSemantics/RegisterStateGeneric.h.

|

overridevirtual |

Removes stored values from the register state.

Depending on the register state implementation, this could either store new, distinct undefined values in each register, or it could simply erase all information about stored values leaving the register state truly empty. For instance RegisterStateGeneric, which uses variable length arrays to store information about a dynamically changing set of registers, clears its arrays to zero length.

Register states can also be initialized by clearing them or by explicitly writing new values into each desired register (or both). See RegisterStateGeneric::initialize_nonoverlapping for one way to initialize that register state.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Set all registers to the zero.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Read a value from a register.

The register descriptor, reg, not only describes which register, but also which bits of that register (e.g., "al", "ah", "ax", "eax", and "rax" are all the same hardware register on an amd64, but refer to different parts of that register). The RISC operations are provided so that they can be used to extract the correct bits from a wider hardware register if necessary.

The dflt value is written into the register state if the register was not defined in the state. By doing this, a subsequent read of the same register will return the same value. Some register states cannot distinguish between a register that was never accessed and a register that was only read, in which case dflt is not used since all registers are already initialized.

See RiscOperators::readRegister for more details.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Read a register without side effects.

This is similar to readRegister except it doesn't modify the register state in any way.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Write a value to a register.

The register descriptor, reg, not only describes which register, but also which bits of that register (e.g., "al", "ah", "ax", "eax", and "rax" are all the same hardware register on an amd64, but refer to different parts of that register). The RISC operations are provided so that they can be used to insert the value bits into a wider the hardware register if necessary. See RiscOperators::readRegister for more details.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Print the register contents.

This emits one line per register and contains the register name and its value.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Merge register states for data flow analysis.

Merges the other state into this state, returning true if this state changed.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

overridevirtual |

Hash the register state.

Hashes the register state by appending its data to the specified hasher.

Implements Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterState.

|

virtual |

Initialize all registers of the dictionary.

When the dictionary contains overlapping registers, only the largest registers are initialized. For example, on a 32-bit x86 architecture EAX would be initialized but not AX, AH, or AL; requesting AX, AH, or AL will return part of the initial EAX value.

|

virtual |

Initialize all registers of the dictionary.

When the dictionary contains overlapping registers, only the smallest registers are initialized. For example, on a 32-bit x86 architecture, AX, AH, AL and the non-named high-order 16 bits of AX are inititialized, but EAX isn't explicitly initialized. Requesting the value of EAX will return a value constructed from the various smaller parts.

| void Rose::BinaryAnalysis::InstructionSemantics2::BaseSemantics::RegisterStateGeneric::initialize_nonoverlapping | ( | const std::vector< RegisterDescriptor > & | , |

| bool | initialize_to_zero | ||

| ) |

Initialize the specified registers of the dictionary.

Each register in the list must not overlap with any other register in the list, or strange things will happen. If initialize_to_zero is set then the specified registers are initialized to zero, otherwise they're initialized with the prototypical value's constructor that takes only a size parameter. This method is somewhat low level and doesn't do much error checking.

|

virtual |

Returns the list of all registers and their values.

The returned registers are guaranteed to be non-overlapping, although they might not correspond to actual named machine registers. For instance, if a 32-bit value was written to the x86 EFLAGS register then the return value will contain a register/value pair for EFLAGS but no pairs for individual flags. If one subsequently writes a 1-bit value to the ZF flag (bit 6 of EFLAGS) then the return value will contain a register/value pair for ZF, and also a pair for bits 0-5, and a pair for bits 7-31, neither of which correspond to actual register names in x86 (there is no name for bits 0-5 as a whole). The readRegister and writeRegister methods can be used to re-cast the various pairs into other groupings; get_stored_registers is a lower-level interface.

|

virtual |

Determines if some of the specified register is stored in the state.

Returns true even if only part of the requested register is in the state (as when one asks about EAX and the state only stores AX). This is slightly more efficient than calling stored_parts():

|

virtual |

Determines if the specified register is wholly stored in the state.

Returns if the state contains data for the entire register, even if that data is split among several smaller parts or exists as a subset of a larger part.

|

virtual |

Determines if the specified register is stored exactly in the state.

Returns true only if the specified register wholly exists and a value can be returned without extracting or concatenating values from larger or smaller stored parts. Note that a value can also be returned without extracting or conctenating if the state contains no data for the specified register, as indicated by is_partly_stored() returning false.

|

virtual |

Returns a description of which bits of a register are stored.

The return value is an ExtentMap that contains the bits that are stored in the state. This does not return the value of any parts of stored registers–one gets that with readRegister. The return value does not contain any bits that are not part of the specified register.

|

virtual |

Find stored registers overlapping with specified register.

Returns all stored registers that overlap with the specified register. The registers in the returned vector will never overlap with each other, but they will all overlap with the specified register.

|

virtual |

Cause a register to not be stored.

Erases all record of the specified register. The RiscOperators pointer is used for its extract operation if the specified register is not exactly stored in the state, such as if the state stores RIP and one wants to erase only the 32-bits overlapping with EIP.

|

virtual |

Traverse register/value pairs.

Traverses all the (non-overlapping) registers and their values, calling the specified functor for each register/value pair. If the functor returns a new SValue then the return value becomes the new value for that register. The new value must have the same width as the register.

For example, the following code performs a symbolic substitution across all the registers:

As with most ROSE and STL traversals, the Visitor is not allowed to modify the structure of the object over which it is traversing. In other words, it's permissible to change the values pointed to by the state, but it is not permissible to perform any operation that might change the list of register parts by adding, removing, or combining parts. This includes calling readRegister and writeRegister except when the register being read or written is already exactly stored in the state as indicated by is_exactly_stored.

|

virtual |

Whether a register has writers.

Returns true if the specified register has writers. The "Any" version returns true if any bits of the register have writers, and the "All" version returns true if all bits of the register have writers (but not necessarily all the same writer).

|

virtual |

Whether a register has writers.

Returns true if the specified register has writers. The "Any" version returns true if any bits of the register have writers, and the "All" version returns true if all bits of the register have writers (but not necessarily all the same writer).

|

virtual |

Get writer information.

Returns all instruction addresses that have written to at least part of the specified register. For instance, if instruction 0x1234 and 0x4321 wrote to AL and instruction 0x5678 wrote to AH then this method would return the set {0x1234, 0x4321, 0x5678} as the writers of AX.

|

virtual |

Get writer information.

Returns the set of instruction addresses that have written to the entire specified register. For instance, if instruction 0x1234 and 0x4321 wrote to AL and instructions 0x1234 and 0x5678 wrote to AH then this method will return the set {0x1234} as the writers of AX.

|

virtual |

Insert writer information.

Adds the specified instruction addresses as writers of the specified register. Any previously existing writer addresses are not affected. Returns true if any addresses were inserted, false if they all already existed. A single writer address can also be specified due to the AddressSet implicit constructor.

|

virtual |

Erase specified writers.

Removes the specified addresses from the set of writers for the register without affecting other addresses that might also be present. Returns true if none of the writer addresses existed, false if any were removed. A single writer address can also be specified due to the AddressSet implicit constructor.

|

virtual |

Set writer information.

Changes the writer information to be exactly the specified address or set of addresses. A single writer address can also be specified due to the AddressSet implicit constructor.

|

virtual |

Erase all writers.

If a register descriptor is provided then all writers are removed for that register only. Otherwise all writers are removed for all registers.

|

virtual |

Erase all writers.

If a register descriptor is provided then all writers are removed for that register only. Otherwise all writers are removed for all registers.

|

virtual |

Whether a register has the specified property.

Returns true if the register has the specified property. The "Any" version returns true if any bits of the register have the property, while the "All" version returns true if all bits of the register have the property.

|

virtual |

Whether a register has the specified property.

Returns true if the register has the specified property. The "Any" version returns true if any bits of the register have the property, while the "All" version returns true if all bits of the register have the property.

|

virtual |

Get properties.

Returns the Boolean properties associated with the specified register. The "Union" version returns the union of the properties across all bits of the register, while the "Intersection" version returns the set of properties that are defined for all bits of the register.

|

virtual |

Get properties.

Returns the Boolean properties associated with the specified register. The "Union" version returns the union of the properties across all bits of the register, while the "Intersection" version returns the set of properties that are defined for all bits of the register.

|

virtual |

Insert Boolean properties.

Inserts the specified properties for all bits of the specified register without affecting any other properties. Returns true if a property was inserted anywhere, false if all specified properties already existed everywhere in the specified register. A single property can also be specified due to the RegisterProperties implicit constructor.

|

virtual |

Erase Boolean properties.

Removes the speciied properties from the specified register. Returns true if any of the properties were erased, false if none of them already existed. A single property can also be specified due to the RegisterProperties implicit constructor.

|

virtual |

Assign property set.

Assigns the specified property set (or single property) to the specified register. The register will then contain only those specified properties.

|

virtual |

Erase all Boolean properties.

Removes all properties from the specified register (or all registers).

|

virtual |

Erase all Boolean properties.

Removes all properties from the specified register (or all registers).

|

virtual |

Get registers having certain properties.

Return a list of registers that have the required properties and lack the prohibited properties. The returned list contains the largest registers that satisfy the conditions.

|

virtual |

Update write properties.

Adds the specified property to all bits of the register. The property can be anything, but is normally either IO_WRITE or IO_INIT depending on whether the writeRegister operation was on behalf of an instruction or not.

|

virtual |

Update read properties.

Adds the READ property to all bits of the register. Also adds READ_BEFORE_WRITE and/or READ_UNINITIALIZED as appropriate depending on writer properties.

Member Data Documentation

|

protected |

Values for registers that have been accessed.

This is a map whose keys are major/minor pairs and whose values are IntervalSetMaps that associate a value with non-overlapping ranges of bits. When reading or writing a register, the register being accessed is guaranteed to overlap only with those registers on the matching major-minor list, if it overlaps at all. The lists are typically short (e.g., one list might refer to all the parts of the x86 RAX register, but the RBX parts would be on a different list. None of the registers stored on a particular list overlap with any other register on that same list; when adding new register that would overlap, the registers with which it overlaps must be removed first.

Definition at line 180 of file BaseSemantics/RegisterStateGeneric.h.

The documentation for this class was generated from the following file:

1.8.10

1.8.10