Description

Semantically evaluates Intel x86 instructions.

Definition at line 33 of file DispatcherX86.h.

#include <Rose/BinaryAnalysis/InstructionSemantics/DispatcherX86.h>

Public Types | |

| enum | AccessMode { READ_REGISTER , PEEK_REGISTER } |

| using | Super = BaseSemantics::Dispatcher |

| Base type. | |

| using | Ptr = DispatcherX86Ptr |

| Shared-ownership pointer. | |

Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| using | Ptr = DispatcherPtr |

| Shared-ownership pointer. | |

Public Member Functions | |

| void | iproc_init () |

| Loads the iproc table with instruction processing functors. | |

| void | regcache_init () |

| Load the cached register descriptors. | |

| void | memory_init () |

| Make sure memory properties are set up correctly. | |

| virtual BaseSemantics::DispatcherPtr | create (const BaseSemantics::RiscOperatorsPtr &) const override |

| Virtual constructor. | |

| virtual RegisterDictionary::RegisterDescriptors | get_usual_registers () const |

| Get list of common registers. | |

| virtual RegisterDescriptor | instructionPointerRegister () const override |

| Returns the instruction pointer register. | |

| virtual RegisterDescriptor | stackPointerRegister () const override |

| Returns the stack pointer register. | |

| virtual RegisterDescriptor | stackFrameRegister () const override |

| Returns the stack call frame register. | |

| virtual int | iprocKey (SgAsmInstruction *insn_) const override |

| Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table. | |

| virtual void | write (SgAsmExpression *e, const BaseSemantics::SValuePtr &value, size_t addr_nbits=0) override |

| Writes to an L-value expression. | |

| virtual void | initializeState (const BaseSemantics::StatePtr &) override |

| Initialize the state. | |

| virtual BaseSemantics::SValuePtr | readRegister (RegisterDescriptor, AccessMode mode=READ_REGISTER) |

| Architecture-specific read from register. | |

| virtual void | writeRegister (RegisterDescriptor, const BaseSemantics::SValuePtr &result) |

| Architecture-specific write to register. | |

| virtual void | setFlagsForResult (const BaseSemantics::SValuePtr &result) |

| Set parity, sign, and zero flags appropriate for result value. | |

| virtual void | setFlagsForResult (const BaseSemantics::SValuePtr &result, const BaseSemantics::SValuePtr &cond) |

| Conditionally set parity, sign, and zero flags appropriate for result value. | |

| virtual BaseSemantics::SValuePtr | parity (const BaseSemantics::SValuePtr &v) |

Returns true if byte v has an even number of bits set; false for an odd number. | |

| virtual BaseSemantics::SValuePtr | invertMaybe (const BaseSemantics::SValuePtr &value, bool maybe) |

Conditionally invert the bits of value. | |

| virtual BaseSemantics::SValuePtr | greaterOrEqualToTen (const BaseSemantics::SValuePtr &value) |

Determines whether value is greater than or equal to ten. | |

| virtual BaseSemantics::SValuePtr | flagsCombo (X86InstructionKind k) |

| Return a Boolean for the specified flag combo for an instruction. | |

| virtual BaseSemantics::SValuePtr | repEnter (X86RepeatPrefix) |

| Enters a loop for a REP-, REPE-, or REPNE-prefixed instruction. | |

| virtual void | repLeave (X86RepeatPrefix, const BaseSemantics::SValuePtr &in_loop, Address insn_va, bool honorZeroFlag) |

| Leave a loop for a REP-, REPE-, or REPNE-prefixed instruction. | |

| virtual BaseSemantics::SValuePtr | doIncOperation (const BaseSemantics::SValuePtr &a, bool dec, bool setCarry) |

| Increments or decrements a value and adjusts flags. | |

| virtual BaseSemantics::SValuePtr | doRotateOperation (X86InstructionKind kind, const BaseSemantics::SValuePtr &operand, const BaseSemantics::SValuePtr &total_rotate, size_t rotateSignificantBits) |

| Implements the RCL, RCR, ROL, and ROR instructions for various operand sizes. | |

| virtual BaseSemantics::SValuePtr | doShiftOperation (X86InstructionKind kind, const BaseSemantics::SValuePtr &operand, const BaseSemantics::SValuePtr &source_bits, const BaseSemantics::SValuePtr &total_shift, size_t shiftSignificantBits) |

| Implements the SHR, SAR, SHL, SAL, SHRD, and SHLD instructions for various operand sizes. | |

| virtual void | pushFloatingPoint (const BaseSemantics::SValuePtr &valueToPush) |

| Push floating-point value onto FP stack. | |

| virtual BaseSemantics::SValuePtr | readFloatingPointStack (size_t position) |

| Read a value from the floating point stack. | |

| virtual void | popFloatingPoint () |

| Pop the top item from the floating point stack. | |

| virtual BaseSemantics::SValuePtr | fixMemoryAddress (const BaseSemantics::SValuePtr &address) const |

| Extend or truncate value to propert memory address width. | |

| virtual BaseSemantics::SValuePtr | saturateSignedToUnsigned (const BaseSemantics::SValuePtr &, size_t narrowerWidth) |

| Convert a signed value to a narrower unsigned type. | |

| virtual BaseSemantics::SValuePtr | saturateSignedToSigned (const BaseSemantics::SValuePtr &, size_t narrowerWidth) |

| Convert a signed value to a narrower signed type. | |

| virtual BaseSemantics::SValuePtr | saturateUnsignedToUnsigned (const BaseSemantics::SValuePtr &, size_t narrowerWidth) |

| Convert an unsigned value to a narrower unsigned type. | |

| X86InstructionSize | processorMode () const |

| CPU mode of operation. | |

| void | processorMode (X86InstructionSize m) |

| CPU mode of operation. | |

| virtual BaseSemantics::SValuePtr | doAddOperation (BaseSemantics::SValuePtr a, BaseSemantics::SValuePtr b, bool invertCarries, const BaseSemantics::SValuePtr &carryIn) |

| Adds two values and adjusts flags. | |

| virtual BaseSemantics::SValuePtr | doAddOperation (BaseSemantics::SValuePtr a, BaseSemantics::SValuePtr b, bool invertCarries, const BaseSemantics::SValuePtr &carryIn, const BaseSemantics::SValuePtr &cond) |

| Adds two values and adjusts flags. | |

Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Public Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| virtual void | processInstruction (SgAsmInstruction *insn) |

| Process a single instruction. | |

| virtual void | processDelaySlot (SgAsmInstruction *delayInsn) |

| Process a delay slot. | |

| virtual InsnProcessor * | iprocLookup (SgAsmInstruction *insn) |

| Lookup the processor for an instruction. | |

| virtual void | iprocReplace (SgAsmInstruction *insn, InsnProcessor *iproc) |

| Replace an instruction processor with another. | |

| virtual void | iprocSet (int key, InsnProcessor *iproc) |

| Set an iproc table entry to the specified value. | |

| virtual InsnProcessor * | iprocGet (int key) |

| Obtain an iproc table entry for the specified key. | |

| Architecture::BaseConstPtr | architecture () const |

| Property: Architecture. | |

| virtual StatePtr | currentState () const |

| Get a pointer to the state object. | |

| virtual SValuePtr | protoval () const |

| Return the prototypical value. | |

| virtual SgAsmInstruction * | currentInstruction () const |

| Returns the instruction that is being processed. | |

| virtual SValuePtr | number_ (size_t nbits, uint64_t number) const |

| Return a semantic value representing a number. | |

| RegisterDictionaryPtr | registerDictionary () const |

| Property: Register dictionary. | |

| virtual RegisterDescriptor | findRegister (const std::string ®name, size_t nbits=0, bool allowMissing=false) const |

| Lookup a register by name. | |

| size_t | addressWidth () const |

| Property: Width of memory addresses in bits. | |

| virtual RegisterDescriptor | callReturnRegister () const |

| Returns the function call return address register. | |

| virtual void | advanceInstructionPointer (SgAsmInstruction *) |

| Update the instruction pointer register. | |

| virtual RegisterDescriptor | segmentRegister (SgAsmMemoryReferenceExpression *) |

| Returns a register descriptor for the segment part of a memory reference expression. | |

| virtual void | incrementRegisters (SgAsmExpression *) |

| Increment all auto-increment registers in the expression. | |

| virtual void | decrementRegisters (SgAsmExpression *) |

| Decrement all auto-decrement registers in the expression. | |

| virtual void | preUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for pre-add expressions. | |

| virtual void | postUpdate (SgAsmExpression *, const BaseSemantics::SValuePtr &enabled) |

| Update registers for post-add expressions. | |

| virtual SValuePtr | effectiveAddress (SgAsmExpression *, size_t nbits=0) |

| Returns a memory address by evaluating the address expression. | |

| virtual SValuePtr | read (SgAsmExpression *, size_t value_nbits=0, size_t addr_nbits=0) |

| Reads an R-value expression. | |

| virtual RiscOperatorsPtr | operators () const |

| Property: RISC operators. | |

| virtual void | operators (const RiscOperatorsPtr &) |

| Property: RISC operators. | |

| virtual SValuePtr | undefined_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| virtual SValuePtr | unspecified_ (size_t nbits) const |

| Return a new undefined semantic value. | |

| bool | autoResetInstructionPointer () const |

| Property: Reset instruction pointer register for each instruction. | |

| void | autoResetInstructionPointer (bool b) |

| Property: Reset instruction pointer register for each instruction. | |

Static Public Member Functions | |

| static DispatcherX86Ptr | instance (const Architecture::BaseConstPtr &) |

| Construct a prototypical dispatcher. | |

| static DispatcherX86Ptr | instance (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) |

| Constructor. | |

| static DispatcherX86Ptr | promote (const BaseSemantics::DispatcherPtr &) |

| Dynamic cast to a DispatcherX86Ptr with assertion. | |

Protected Member Functions | |

| DispatcherX86 (const Architecture::BaseConstPtr &) | |

| DispatcherX86 (const Architecture::BaseConstPtr &, const BaseSemantics::RiscOperatorsPtr &) | |

Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Member Functions inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| Dispatcher (const Architecture::BaseConstPtr &) | |

| Dispatcher (const Architecture::BaseConstPtr &, const RiscOperatorsPtr &) | |

| virtual void | processCommon () |

Protected Attributes | |

| X86InstructionSize | processorMode_ |

Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Attributes inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| bool | autoResetInstructionPointer_ = true |

| Reset instruction pointer register for each instruction. | |

| InsnProcessors | iproc_table |

Additional Inherited Members | |

Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher Protected Types inherited from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher | |

| typedef std::vector< InsnProcessor * > | InsnProcessors |

Member Typedef Documentation

◆ Super

Base type.

Definition at line 36 of file DispatcherX86.h.

◆ Ptr

Shared-ownership pointer.

Definition at line 39 of file DispatcherX86.h.

Member Enumeration Documentation

◆ AccessMode

| enum Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::AccessMode |

Definition at line 159 of file DispatcherX86.h.

Member Function Documentation

◆ iproc_init()

| void Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::iproc_init | ( | ) |

Loads the iproc table with instruction processing functors.

This normally happens from the constructor.

◆ regcache_init()

| void Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::regcache_init | ( | ) |

Load the cached register descriptors.

This happens at construction and when the registerDictionary property is changed.

◆ memory_init()

| void Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::memory_init | ( | ) |

Make sure memory properties are set up correctly.

For instance, byte order should be little endian.

◆ instance()

|

static |

Construct a prototypical dispatcher.

The only thing this dispatcher can be used for is to create another dispatcher with the virtual create method.

◆ create()

|

overridevirtual |

Virtual constructor.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ processorMode() [1/2]

|

inline |

CPU mode of operation.

Definition at line 144 of file DispatcherX86.h.

◆ processorMode() [2/2]

|

inline |

CPU mode of operation.

Definition at line 145 of file DispatcherX86.h.

◆ get_usual_registers()

|

virtual |

Get list of common registers.

Returns a list of non-overlapping registers composed of the largest registers except using individual flags for the fields of the FLAGS/EFLAGS register.

◆ instructionPointerRegister()

|

overridevirtual |

Returns the instruction pointer register.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ stackPointerRegister()

|

overridevirtual |

Returns the stack pointer register.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ stackFrameRegister()

|

overridevirtual |

Returns the stack call frame register.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ iprocKey()

|

overridevirtual |

Given an instruction, return the InsnProcessor key that can be used as an index into the iproc_table.

Implements Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ write()

|

overridevirtual |

Writes to an L-value expression.

The expression can be a register or memory reference. The width of the address passed to lower-level memory access functions is specified by addr_nbits. If addr_nbits is zero then the natural width of the effective address is passed to lower level functions.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ initializeState()

|

overridevirtual |

Initialize the state.

Some architectures benefit from having their initial state initialized in a certain way. For instance, on x86/amd64 the segment registers CS, DS, and SS typically refer to the entire machine memory and can be initialized to have a zero base address.

Reimplemented from Rose::BinaryAnalysis::InstructionSemantics::BaseSemantics::Dispatcher.

◆ readRegister()

|

virtual |

Architecture-specific read from register.

Similar to RiscOperators::readRegister, but might do additional architecture-specific things.

◆ writeRegister()

|

virtual |

Architecture-specific write to register.

Similar to RiscOperators::writeRegister, but might do additional architecture-specific things. For instance, writing to a 32-bit GPR such as "eax" on x86-64 will write zeros to the upper half of "rax".

◆ invertMaybe()

|

virtual |

Conditionally invert the bits of value.

The bits are inverted if maybe is true, otherwise value is returned.

◆ repEnter()

|

virtual |

Enters a loop for a REP-, REPE-, or REPNE-prefixed instruction.

The return value is true if ECX is non-zero or the instruction doesn't have repeat prefix, and false otherwise. Use this in conjunction with repLeave().

◆ repLeave()

|

virtual |

Leave a loop for a REP-, REPE-, or REPNE-prefixed instruction.

The in_loop argument is the Boolean that indicates whether we just executed the instruction, and is usually the return value from the previous repEnter() call. If in_loop is false then this function is a no-op. Otherwise, the ECX register is decremented and, if it is non-zero and the repeat condition (true, equal, or not-equal) is satisified, then the EIP register is reset to the specified instruction address causing the instruction to be repeated. Use this in conjunction with repEnter(). The REP and REPE prefixes are shared, both represented by x86_repeat_repe, and we use the honorZeroFlag to decide whether the prefix is REP (false) or REPE (true).

◆ doAddOperation() [1/2]

|

virtual |

Adds two values and adjusts flags.

This method can be used for subtraction if b is two's complement and invertCarries is set. If cond is supplied, then the addition and flag adjustments are conditional.

◆ doAddOperation() [2/2]

|

virtual |

Adds two values and adjusts flags.

This method can be used for subtraction if b is two's complement and invertCarries is set. If cond is supplied, then the addition and flag adjustments are conditional.

◆ doIncOperation()

|

virtual |

Increments or decrements a value and adjusts flags.

If dec is set then the value is decremented instead of incremented. If setCarry is set then the CF flag is affected.

◆ doRotateOperation()

|

virtual |

Implements the RCL, RCR, ROL, and ROR instructions for various operand sizes.

The rotate amount is always 8 bits wide in the instruction, but the semantics mask off all but the low-order bits, keeping 5 bits in 32-bit mode and 6 bits in 64-bit mode (indicated by the rotateSignificantBits argument).

◆ doShiftOperation()

|

virtual |

Implements the SHR, SAR, SHL, SAL, SHRD, and SHLD instructions for various operand sizes.

The shift amount is always 8 bits wide in the instruction, but the semantics mask off all but the low-order bits, keeping 5 bits in 32-bit mode and 7 bits in 64-bit mode (indicated by the shiftSignificantBits argument). The semantics of SHL and SAL are identical (in fact, ROSE doesn't even define x86_sal). The source_bits argument contains the bits to be shifted into the result and is used only for SHRD and SHLD instructions.

◆ pushFloatingPoint()

|

virtual |

Push floating-point value onto FP stack.

Pushes the specified value onto the floating-point circular stack. The current top-of-stack is the REG_ST register, but whose minor number is the value stored in the REG_ST_TOP register. The value in REG_ST_TOP (which must be concrete) is decremented modulo eight before being used.

◆ saturateSignedToUnsigned()

|

virtual |

Convert a signed value to a narrower unsigned type.

Returns the truncated source value except when the value cannot be represented in the narrower type, in which case the closest unsigned value is returned (zero or all bits set).

◆ saturateSignedToSigned()

|

virtual |

Convert a signed value to a narrower signed type.

Returns the truncated source value except when the value cannot be represented by the narrower type, in which case the closest signed value is returned. The closest signed value is either 0b1000...0 (minimum signed value) or 0b0111...1 (maximum signed value).

◆ saturateUnsignedToUnsigned()

|

virtual |

Convert an unsigned value to a narrower unsigned type.

Returns the truncated source value except when the value cannot be represented by the narrower type, in which case the closest unsigned value is returned.

Member Data Documentation

◆ processorMode_

|

protected |

Definition at line 42 of file DispatcherX86.h.

◆ REG_anyAX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyAX |

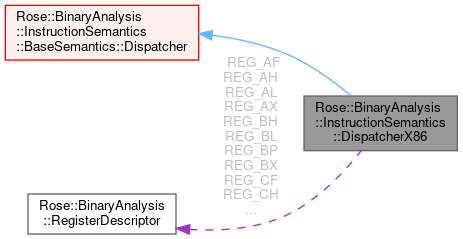

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 53 of file DispatcherX86.h.

◆ REG_anyBX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyBX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 53 of file DispatcherX86.h.

◆ REG_anyCX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyCX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 53 of file DispatcherX86.h.

◆ REG_anyDX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyDX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 53 of file DispatcherX86.h.

◆ REG_RAX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RAX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 54 of file DispatcherX86.h.

◆ REG_RBX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RBX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 54 of file DispatcherX86.h.

◆ REG_RCX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RCX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 54 of file DispatcherX86.h.

◆ REG_RDX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RDX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 54 of file DispatcherX86.h.

◆ REG_EAX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EAX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 55 of file DispatcherX86.h.

◆ REG_EBX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EBX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 55 of file DispatcherX86.h.

◆ REG_ECX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ECX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 55 of file DispatcherX86.h.

◆ REG_EDX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EDX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 55 of file DispatcherX86.h.

◆ REG_AX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_AX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 56 of file DispatcherX86.h.

◆ REG_BX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_BX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 56 of file DispatcherX86.h.

◆ REG_CX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_CX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 56 of file DispatcherX86.h.

◆ REG_DX

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DX |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 56 of file DispatcherX86.h.

◆ REG_AL

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_AL |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 57 of file DispatcherX86.h.

◆ REG_BL

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_BL |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 57 of file DispatcherX86.h.

◆ REG_CL

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_CL |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 57 of file DispatcherX86.h.

◆ REG_DL

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DL |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 57 of file DispatcherX86.h.

◆ REG_AH

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_AH |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 58 of file DispatcherX86.h.

◆ REG_BH

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_BH |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 58 of file DispatcherX86.h.

◆ REG_CH

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_CH |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 58 of file DispatcherX86.h.

◆ REG_DH

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DH |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 58 of file DispatcherX86.h.

◆ REG_R8

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R8 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 60 of file DispatcherX86.h.

◆ REG_R9

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R9 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 60 of file DispatcherX86.h.

◆ REG_R10

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R10 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 60 of file DispatcherX86.h.

◆ REG_R11

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R11 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 60 of file DispatcherX86.h.

◆ REG_R12

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R12 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 61 of file DispatcherX86.h.

◆ REG_R13

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R13 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 61 of file DispatcherX86.h.

◆ REG_R14

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R14 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 61 of file DispatcherX86.h.

◆ REG_R15

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_R15 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 61 of file DispatcherX86.h.

◆ REG_anyDI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyDI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 63 of file DispatcherX86.h.

◆ REG_anySI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anySI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 63 of file DispatcherX86.h.

◆ REG_anySP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anySP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 63 of file DispatcherX86.h.

◆ REG_anyBP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyBP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 63 of file DispatcherX86.h.

◆ REG_anyIP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyIP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 63 of file DispatcherX86.h.

◆ REG_RDI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RDI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 64 of file DispatcherX86.h.

◆ REG_RSI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RSI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 64 of file DispatcherX86.h.

◆ REG_RSP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RSP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 64 of file DispatcherX86.h.

◆ REG_RBP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RBP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 64 of file DispatcherX86.h.

◆ REG_RIP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RIP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 64 of file DispatcherX86.h.

◆ REG_EDI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EDI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 65 of file DispatcherX86.h.

◆ REG_ESI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ESI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 65 of file DispatcherX86.h.

◆ REG_ESP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ESP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 65 of file DispatcherX86.h.

◆ REG_EBP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EBP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 65 of file DispatcherX86.h.

◆ REG_EIP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EIP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 65 of file DispatcherX86.h.

◆ REG_DI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 66 of file DispatcherX86.h.

◆ REG_SI

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_SI |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 66 of file DispatcherX86.h.

◆ REG_SP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_SP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 66 of file DispatcherX86.h.

◆ REG_BP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_BP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 66 of file DispatcherX86.h.

◆ REG_IP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_IP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 66 of file DispatcherX86.h.

◆ REG_CS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_CS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_DS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_ES

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ES |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_SS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_SS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_FS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_FS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_GS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_GS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 68 of file DispatcherX86.h.

◆ REG_anyFLAGS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_anyFLAGS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 70 of file DispatcherX86.h.

◆ REG_RFLAGS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_RFLAGS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 70 of file DispatcherX86.h.

◆ REG_EFLAGS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_EFLAGS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 70 of file DispatcherX86.h.

◆ REG_FLAGS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_FLAGS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 70 of file DispatcherX86.h.

◆ REG_AF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_AF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_CF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_CF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_DF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_DF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_OF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_OF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_PF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_PF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_SF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_SF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_TF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_TF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_ZF

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ZF |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 71 of file DispatcherX86.h.

◆ REG_ST0

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_ST0 |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 73 of file DispatcherX86.h.

◆ REG_FPSTATUS

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_FPSTATUS |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 73 of file DispatcherX86.h.

◆ REG_FPSTATUS_TOP

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_FPSTATUS_TOP |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 73 of file DispatcherX86.h.

◆ REG_FPCTL

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_FPCTL |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 73 of file DispatcherX86.h.

◆ REG_MXCSR

| RegisterDescriptor Rose::BinaryAnalysis::InstructionSemantics::DispatcherX86::REG_MXCSR |

Cached register.

This register is cached so that there are not so many calls to Dispatcher::findRegister(). The register descriptor is updated only when the registerDictionary property is changed.

Register names like REG_anyAX have sizes that depend on the architecture: 16 bits for 16-bit architectures, 32 bits for 32-bit architectures, etc. The other register names have specific sizes–such as REG_EAX being 32 bits–and are defined only on architectures that support them.

Definition at line 73 of file DispatcherX86.h.

The documentation for this class was generated from the following file: